## MQ-1100/1132 LCD and Peripheral Controller

**Datasheet**

**Preliminary Version**

**August 16, 2001**

### **Revision History**

The following table constitutes the revisions to this document as of August 16, 2001. **REVISION HISTORY TABLE: Latest Document Revisions**

| DATE            | Chapter                                     | Revision Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|-----------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| August 16, 2001 | Chapter 2                                   | Removed reference to external 3.3V clock oscillator from OSCFO pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| August 16, 2001 | Chapter 5                                   | Corrected load current for VOL & VOH spcification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| June 8, 2001    | Formatting updates throughout the datasheet | The revisions found in this version of the datasheet are the latest revisions for this datasheet.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| June 6, 2001    | Chapter 6                                   | Added figure and table, see Figure 6-11 anf Table 6-11.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| June 6, 2001    | Chapter 4                                   | Changed bit definitions in Register 4-31 through Register 4-58                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| June 6, 2001    | Chapter 4                                   | Corrected typogrphic error in <i>Table 4-8</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| June 6, 2001    | Chapter 5                                   | Changed specifications in <i>Table 5-3</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| April 30, 2001  | Chapter 4                                   | Added Bit Values and Value Definitions to Bit 4:0, Register 4-75.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| April 30, 2001  | Chapter 2                                   | Added GPIO6 for Motorola DragonBall 100=pin TQFP number 42, in <i>Table 2-22</i> . Changed GPIO values for 132-pin BGA, B3, N3, N4, N14, in <i>Table 2-22</i> .                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| April 30, 2001  | Chapter 4                                   | Revised section "DMA Transfer and DMA Registers" on page 161.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| April 29, 2001  | Revision History<br>Section                 | Updated references and links in this section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| April 23, 2001  | Chapter 3                                   | Revised Figure 3-8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| April 23, 2001  | Chapter 2                                   | Changed descriptions of pin OSCFI and pin OSCFO in Table 2-2.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| April 23, 2001  | Chapter 4                                   | Added name to Register 4-1 through Register 4-8. Revised Section 4.9.1", General Description and Architecture." Changed Table 4-7. Changed bit definition [2:0] and 6:4] in Register 4-32. Added note after Register 4-74 and Register 4-82. Added Figure 4-4. Added Table 4-4. Changed Figure 4-1 and Figure 4-5.                                                                                                                                                                                                  |  |  |  |

| April 22, 2001  | Chapter 4                                   | Added Offsets to all the registers. Added <i>Figure 4-1</i> and <i>Figure 4-2</i> . Revised Bit Definition <i>Register 4-2</i> , bit 10. Revised Section 4.4. Changed <i>Figure 4-3</i> .                                                                                                                                                                                                                                                                                                                           |  |  |  |

| April 20, 2001  | Chapter 5                                   | Changed specifications for <i>Table 5-4</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| April 15, 2001  | Chapter 1                                   | Added FVSYNC label to Figure 1-1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| April 10, 2001  | Chapter 6                                   | Changed Figure 6-7, Figure 6-8, Figure 6-9, Figure 6-10 and added specifications to Table 6-4. Table 6-5. Table 6-8. and Table 6-10.                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| April 9, 2001   | Chapter 2                                   | <i>Table 2-11.</i> added MQ-1100 Ball Number for pin UWE#. Changed Type designations in <i>Table 2-13. Table 2-14. Table 2-18.</i> and <i>Table 2-19.</i>                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| April 8, 2001   | Chapter 3                                   | Changed Figure 3-1 and Figure 3-8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

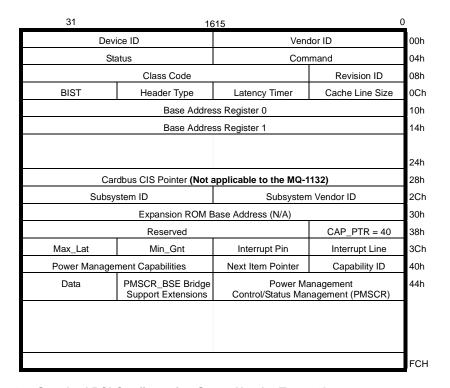

| April 8, 2001   | Chapter 4                                   | Revised section "Interrupt Controller" on page 79. Changed figure "Standard PCI Configuration Space Header Type 00h" on page 83.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| April 4, 2001   | Chapter 5                                   | Changed and added specifications in Table 5-4, "DC Characteristics," on page 236.                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| April 4, 2001   | Chapter 4                                   | Added Register 4-70, "Flat Panel Additional Pin Output Select (FP0BR: Index: 2Ch, Offset 62Ch)," on page 124 Changed Table 4-2, "Device Configuration Register Index and Reset Values," on page 66. Bit 10 changed in Register 4-2, "Device Configuration Register 1 (DC01R: Index 04h, Offset 384h)," on page 67.                                                                                                                                                                                                  |  |  |  |

| March 30, 2001  | Chapter 6                                   | Note added after Table 6-3. Intel SA11xx Read and after Table 6-4. Intel SA11xx Write.                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| March 30, 2001  | Chapter 5                                   | Table 5-3. Power Dissipation by Function, changed and added values; Table 5-4., changed and added values.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| March 30, 2001  | Chapter 4                                   | Register 4-5, "Device Configuration Register 4 (DC04R: Index 10h, Offset 390h)," on page 68, some bits designated as MQ-1132 only; re-wrote section 4.4, Interrupt Controller; re-wrote section 4.7.1; Register 4-34, bit 31:26, changed bit definition; Register 4-31, bit 27:24, changed bit definition; Register 4-61, bit 22, changed value definition. Added textual explanation on page 115. Note added to Register 4-165, "SPI Module FIFO Threshold Register (SP06R: Index 18h, Offset 318h)," on page 206. |  |  |  |

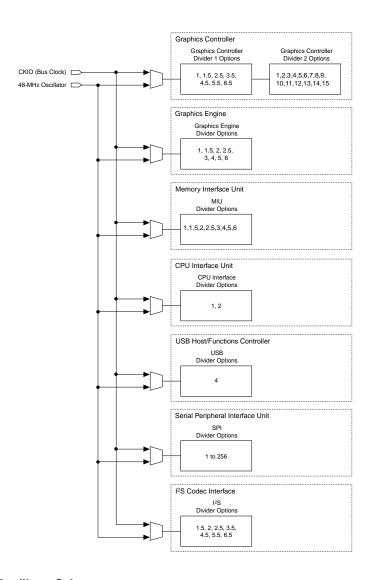

| March 30, 2001  | Chapter 3                                   | Figure 3-3, changed specifications for Graphics Controller Divider 2 Options; added Figure 3-16, Generic TFT Timing and accompanying table, see Table 3-4.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

#### **REVISION HISTORY TABLE: Latest Document Revisions**

| DATE           | Chapter   | Revision Comments                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| March 30, 2001 | Chapter 2 | Changes to <i>Table 2-2</i> . (see CGND description); <i>Table 2-3</i> ., see Type designation, Pin MD; <i>Table 2-4</i> . <i>Table 2-5</i> . changed Type description, <i>Table 2-7</i> . changed Type description; <i>Table 2-9</i> . changed Type description; <i>Table 2-11</i> . see Pin LWE#; <i>Table 2-13</i> . changed Type description; <i>Table 2-17</i> . see Pin BVDD and BGND; <i>Table 2-22</i> . (see 100-Pin TQFP). |

| March 30, 2001 | Chapter 1 | Changes to Figure 1-1 (see labels and GPIO designations).                                                                                                                                                                                                                                                                                                                                                                            |

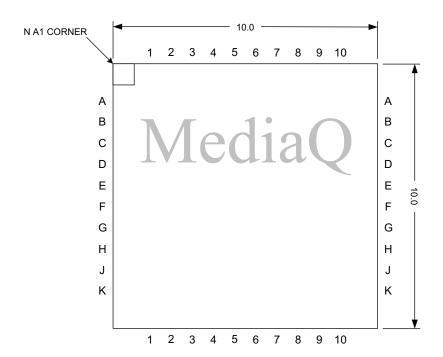

| March 22, 2001 | Chapter 2 | New pin numbers were added to reflect the MQ-1100 BGA package. New figures were added to correspond to the MQ-1100, 100-pin package.                                                                                                                                                                                                                                                                                                 |

# MediaQ<sup>™</sup> Incorporated 2975 San Ysidro Way Santa Clara California 95051

Copyright© 2001 All rights reserved. MediaQ, Incorporated. MediaQ, MediaQ logo, DynamiQ, and Qview are trademarks and/or service marks of MediaQ, Incorporated in the United States and other countries. Other brands or products are trademarks of their respective holders. The specifications contained herein are subject to change without notice. MediaQ assumes no responsibility or liability arising out of the application or use of any information, product or service described herein except as expressly agreed to in writing by MediaQ, Incorporated. MediaQ customers are advised to obtain the latest version of the device specifications before relying on any published information and before placing orders for products or services. All rights reserved.

## **Table of Contents**

| Latest Document Revisions                             | 11 |

|-------------------------------------------------------|----|

| Chapter 1                                             | 1  |

| LCD and Peripheral Controller Overview                | 1  |

| Chapter 2                                             |    |

| Pin and Package Descriptions                          |    |

| Pin Descriptions                                      |    |

| Package Descriptions                                  |    |

| MQ-1100 BGA Package Designs                           |    |

| MQ-1100 BGA Fackage Designs                           |    |

| MQ-1132 BGA Package Designs                           |    |

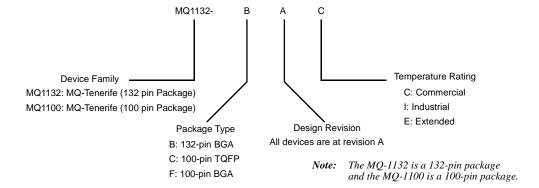

| Part Numbering                                        |    |

| -                                                     |    |

| Chapter 3                                             | 29 |

| Functional Description                                | 29 |

| CPU Interface                                         | 31 |

| PCI Bus interface                                     |    |

| Interrupt Controller                                  | 32 |

| Clocks and Oscillators                                |    |

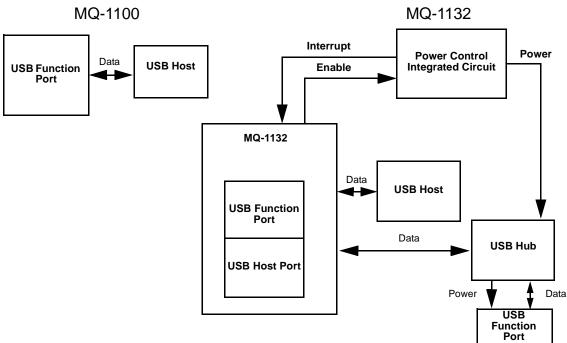

| Universal Serial Bus (USB)                            |    |

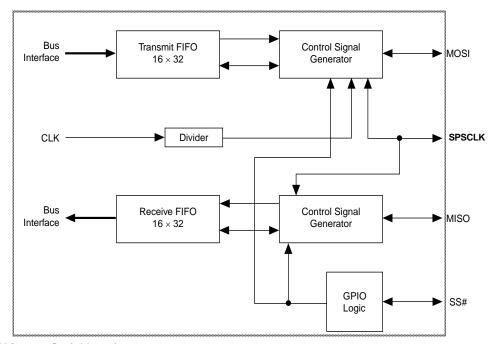

| Serial Peripheral Interface (SPI)                     |    |

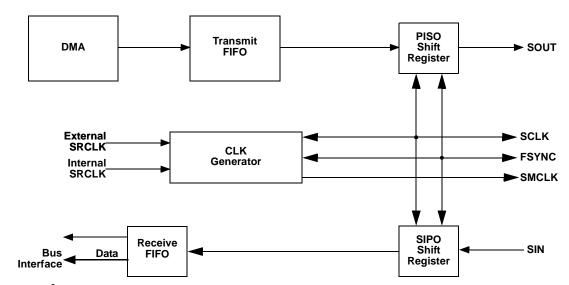

| I2S Codec Interface                                   |    |

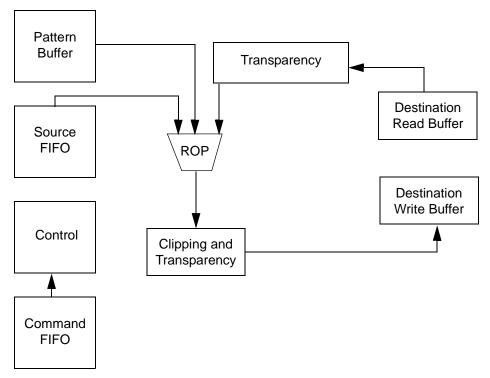

| Graphics Engine                                       |    |

| Theory of Operation                                   |    |

| Raster Operation                                      |    |

| Clipping and Transparency                             |    |

| Bresenham Line Draw                                   | 40 |

| Monochrome to Color Expansion                         | 41 |

| Graphics Engine Register Set                          | 41 |

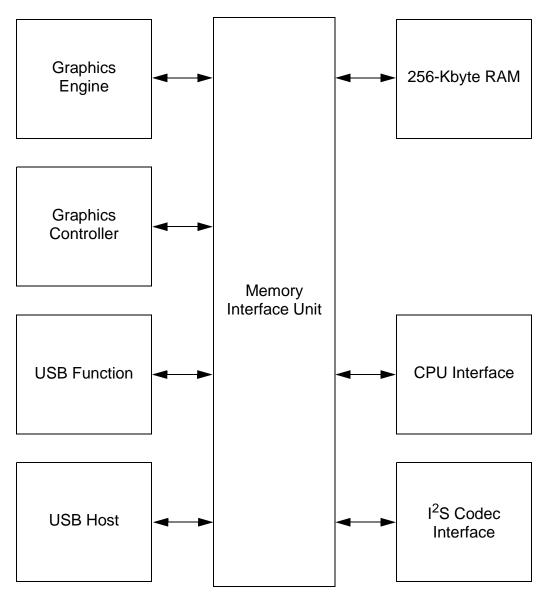

| Memory Interface Unit                                 | 42 |

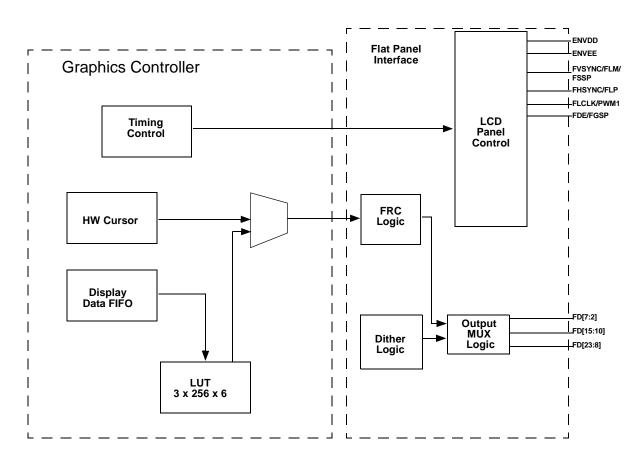

| Display Section                                       |    |

| Theory of Operation                                   |    |

| Flat Panel Interface                                  |    |

| Signal to Pin Mapping for Color and Monochrome Panels |    |

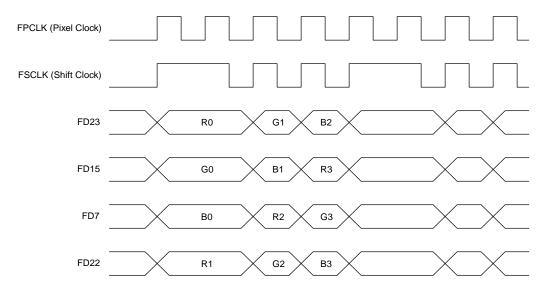

| Timing Diagrams for STN Panels                        | 47 |

| Chapter 4 |                                                         | 53  |

|-----------|---------------------------------------------------------|-----|

| Programmi | ing Information                                         | 53  |

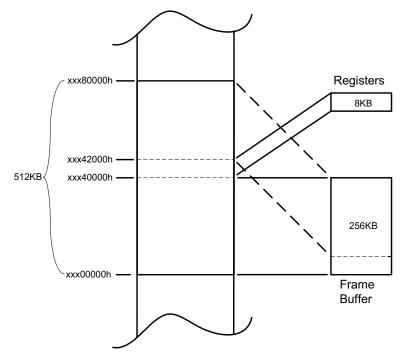

|           | MQ-1100/1132 Address Map (Microprocessor Interfaces)    | 53  |

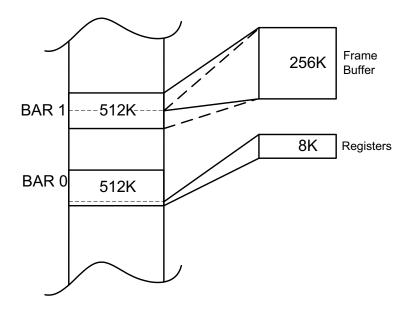

|           | MQ-1100/1132 Address Map (PCI)                          | 54  |

|           | Register Mapping                                        |     |

|           | Registers Implemented in the CPU Configuration Module   |     |

|           | Device Configuration Registers                          | 56  |

|           | CPU Interface Registers                                 | 61  |

|           | Interrupt Controller                                    | 69  |

|           | Interrupt Controller Registers                          | 69  |

|           | PCI Registers                                           |     |

|           | Registers in the Configuration Space                    | 74  |

|           | Memory Interface Unit                                   | 77  |

|           | Graphics Controller                                     | 80  |

|           | General Description and Architecture                    | 80  |

|           | Graphics Controller Register Definition                 | 83  |

|           | Graphics Controller Color Palette                       |     |

|           | Flat-Panel Interface                                    | 97  |

|           | Flat-Panel Register Definition                          |     |

|           | Graphics Engine Programming                             |     |

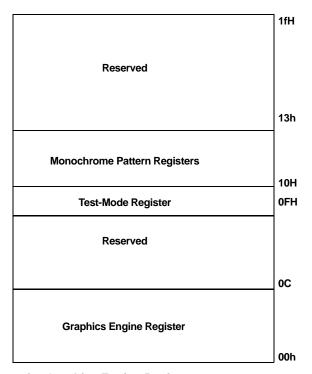

|           | Graphics Engine Module Register Set List                |     |

|           | Graphics Engine Register Definition                     | 123 |

|           | USB Function                                            |     |

|           | Suspend and Resume Logic                                |     |

|           | DMA Transfer and DMA Registers                          |     |

|           | USB Host Module (MQ-1132 only)                          |     |

|           | OHCI Registers                                          |     |

|           | Root Hub Partition                                      |     |

|           | Serial Peripheral Interface Module (MQ-1132 only)       |     |

|           | Transmit Operation                                      |     |

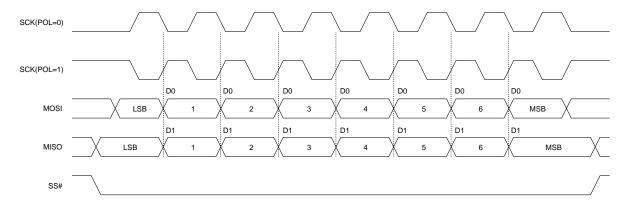

|           | Receive Operation  Details of the Data Transfer Formats |     |

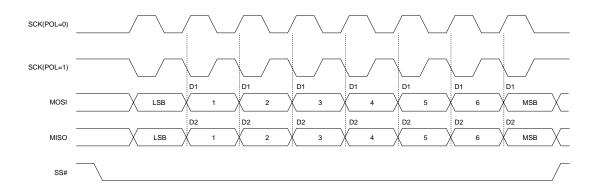

|           | CPHA = 1 Transfer Format                                |     |

|           | Data Transfer – in Progress and Completion              |     |

|           | Master Mode                                             |     |

|           | Slave Mode                                              |     |

|           | Fault Condition Detection                               |     |

|           | Synchronous Serial Channel (I2S) (MQ-1132 only)         | 206 |

|           | Register Definitions                                    |     |

| Chapter 5 |                                                         | 225 |

| DC Charac | eteristics                                              | 225 |

|           | DC Characteristics - Tables and Specifications          | 225 |

|           |                                                         |     |

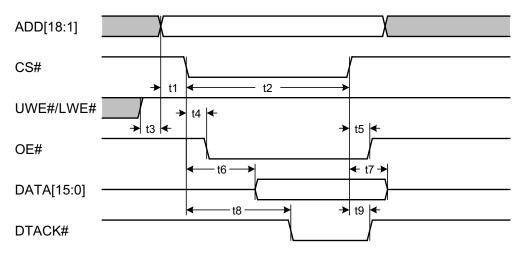

| Chapter 6 |                   | <br> |       | 227 |

|-----------|-------------------|------|-------|-----|

| AC Timin  | g Characteristics | <br> | ••••• | 227 |

MQ-1100/1132, LCD and Peripheral Controller Table of Contents

## **List of Tables**

| Chapter 1 1                                                           |

|-----------------------------------------------------------------------|

| Chapter 2                                                             |

| MQ-110/MQ-1132 Pin Types 3                                            |

| MQ-1100 and MQ-1132 Clock Pins 3                                      |

| MQ-1100 and MQ-1132, Reset and Mode Control Pins 4                    |

| MQ-1100 and MQ-1132, Hitachi SH 7709 and SH 7750 Bus Interface Pins 5 |

| Additional MQ-1132 Reset and Mode Control Pins 5                      |

| Additional MQ-1132, Hitachi SH 7709 and SH 7750, Bus Interface Pins 6 |

| MQ-1100 and MQ-1132 NEC VR-4111 and VR-4121 Bus Interface Pins 7      |

| MQ-1100/1132, Intel SA-110 and SA-2 Bus Interface Pins 8              |

| Additional MQ-1132, NEC VR-4111 and VR-4121 Bus Interface Pins 8      |

| Additional MQ-1132, Intel SA-1110 XScale CPU Bus Interface Pins 9     |

| MQ-1100/1132, Motorola DragonBall Series Bus Interface Pins 9         |

| Additional MQ-1132 Motorola DragonBall Series Bus Interface Pins 10   |

| MQ-1132 PCI Bus Interface Pins 10                                     |

| MQ-1100/1132 FPI Pins 12                                              |

| Additional MQ-1132 FPI Pins 14                                        |

| MQ-1132 USB Interface Pins 15                                         |

| MQ-1132 Additional USB Host Interface Pins 15                         |

| MQ-1132 I2C Codec Interface Pins 15                                   |

| MQ-1132 LED, SPI, and GPIO Pins 16                                    |

| MQ-1132 GPIO Pins 17                                                  |

| MQ-1100/1132 Pin Order and Assignments 18                             |

| CPU Mode Pin Settings 18                                              |

| Chapter 3                                                             |

| I2S Interface Pins 38                                                 |

| Signal Pin Mapping for Color Panels 45                                |

| Signal Pin Mapping for Monochrome Panels 46                           |

| 320 x 320 TFT Panel Horizontal and Vertical Timings                   |

| Chapter 4                                                 | 53  |

|-----------------------------------------------------------|-----|

| MQ-1100/1132 Register Mapping                             | 55  |

| Device Configuration Register Index and Reset Values      | 56  |

| CPU Interface Registers                                   |     |

| Interrupt Controller Register Index and Reset Values      | 69  |

| Index of Configuration Space Registers                    | 73  |

| MIU Register Index and Reset Values                       | 77  |

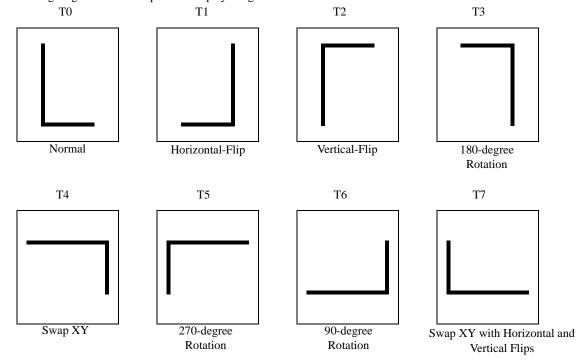

| Display Image Transformation                              | 81  |

| Graphics Controller Memory Requirements                   | 82  |

| Graphics Controller Register Index and Reset Values       | 83  |

| Flat-Panel Register Index and Reset Values                | 98  |

| Graphics Engine Register Index and Reset Values           | 123 |

| USB Register Index and Reset Values                       | 135 |

| Additional USB Register Index and Reset Values            |     |

| Host Controller Operation Register Index and Reset Values |     |

| SPI Register Index and Reset Values                       |     |

| I2S Register Index and Reset Values                       | 207 |

| Chapter 5                                                 | 225 |

| Absolute Maximum Conditions                               | 225 |

| Normal Operating Conditions                               | 225 |

| Power Dissipation by Function                             |     |

| DC Characteristics                                        |     |

| Chapter 6                                                 | 227 |

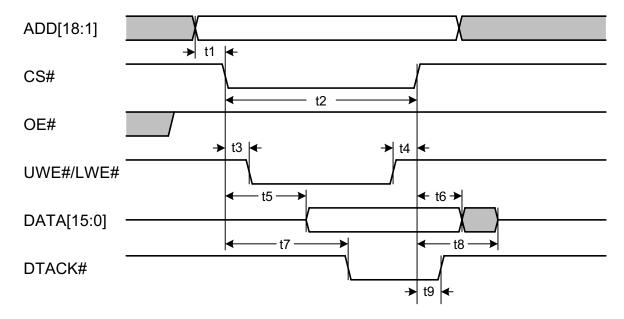

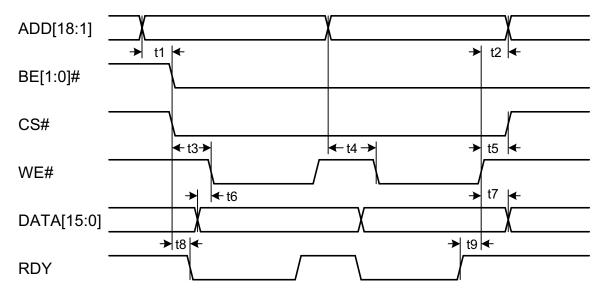

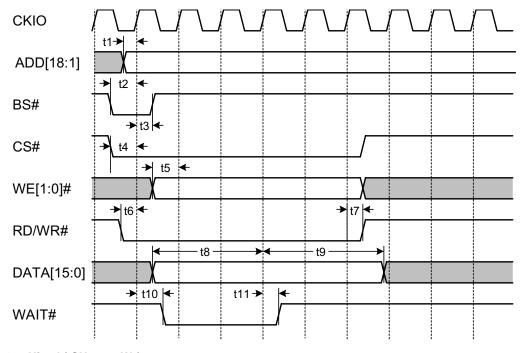

| Motorola Dragonball Read                                  | 227 |

| Motorola Dragonball Write                                 |     |

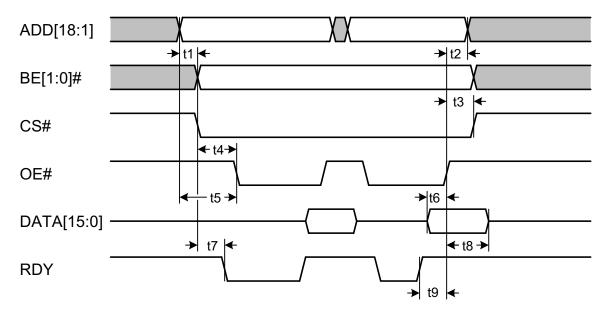

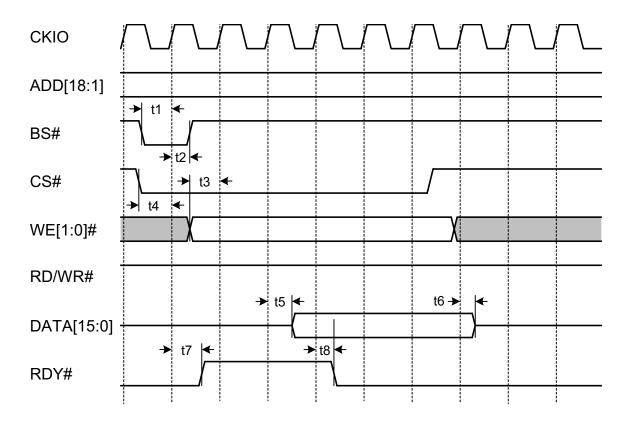

| Intel SA11xx Read                                         |     |

| Intel SA11xx Write                                        |     |

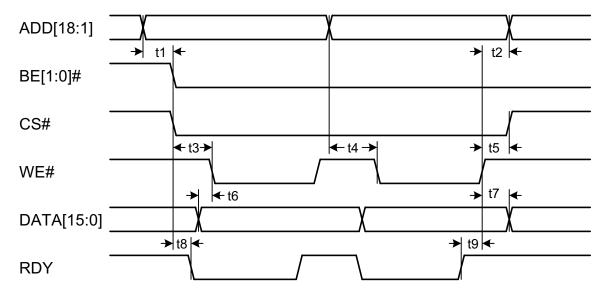

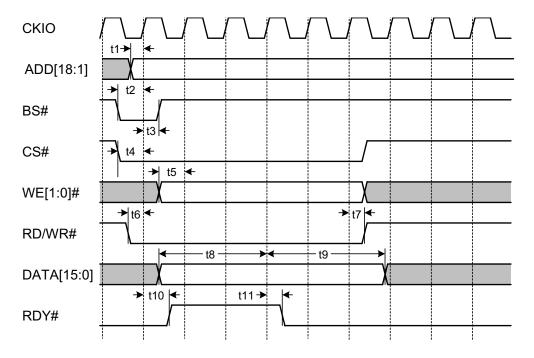

| NEC 41xx Read                                             |     |

| NEC 41xx Write                                            |     |

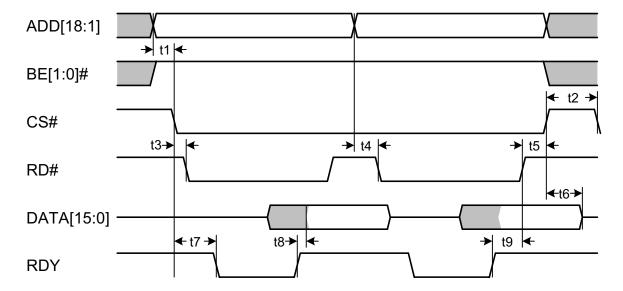

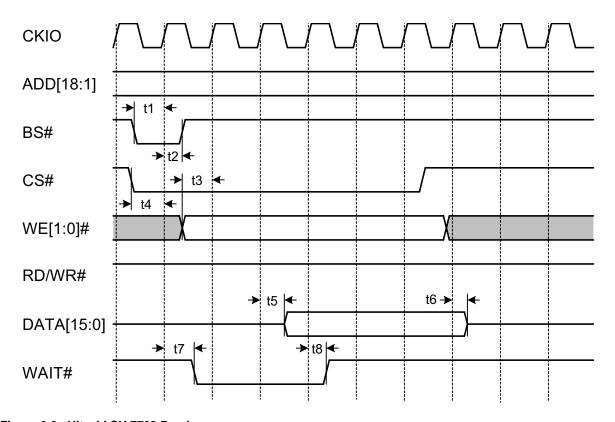

| Hitachi SH 7750 Read                                      |     |

| Hitachi SH 7750 Write                                     |     |

| Hitachi SH 7709 Read                                      |     |

| Hitachi SH 7709 Write                                     |     |

## **List of Figures**

| Chapter 1                                                        | 1  |

|------------------------------------------------------------------|----|

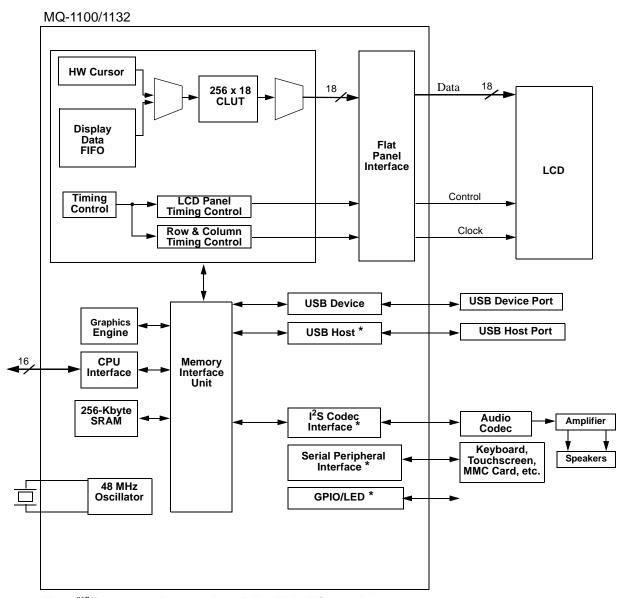

| MQ-1100/1132 Block Diagram                                       | 2  |

| Chapter 2                                                        | 3  |

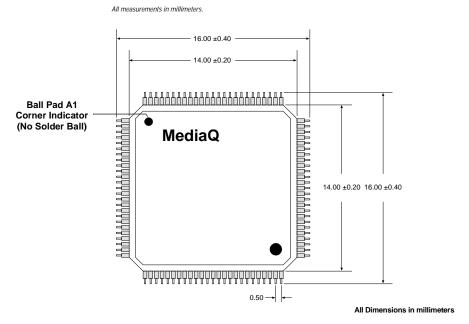

| MQ-1100 – BGA Package Top View with Dimensions in Millimeters    | 23 |

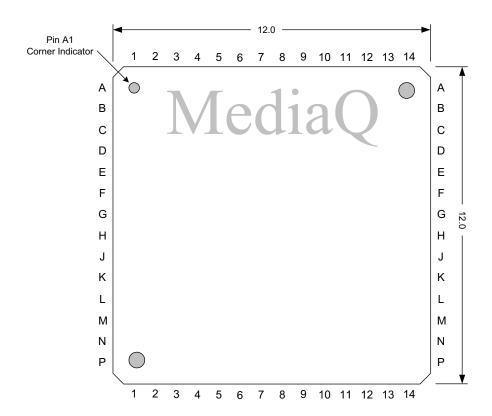

| MQ-1100 BGA Package - Bottom View with Dimensions in Millimeters |    |

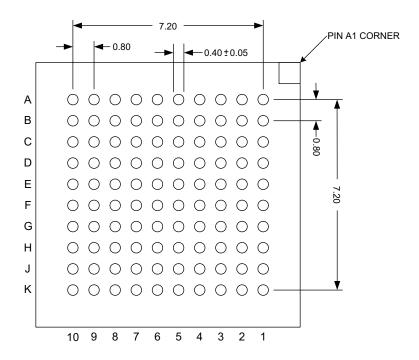

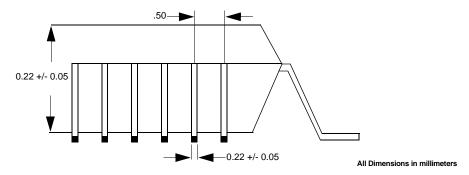

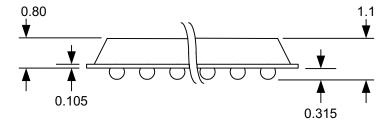

| MQ-1100 BGA Package – Side View with Dimensions in Millimeters   | 24 |

| MQ-1100 TQFP – Dimensions and Package Top View                   | 25 |

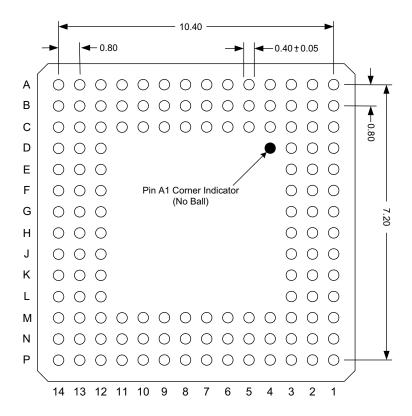

| MQ-1132 BGA Package Top View with Dimensions in Millimeters      | 26 |

| MQ-1132 BGA Package – Bottom View with Dimensions in Millimeters | 27 |

| MQ-1132 BGA Package – Side View with Dimensions in Millimeters   | 27 |

| Part Number Definition                                           | 28 |

| Chapter 3                                                        | 29 |

| MQ-1100/1132 Block Diagram                                       | 30 |

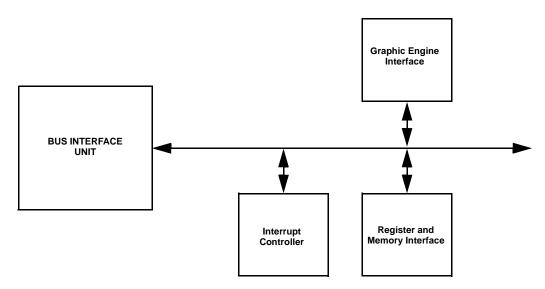

| MQ-1132 CPU Interface                                            |    |

| Clock and Oscillator Scheme                                      |    |

| MQ-1100/1132 USB Functionality                                   | 35 |

| MQ-1132 Serial Interface                                         |    |

| I <sup>2</sup> S Codec Interface                                 |    |

| Graphics Engine                                                  | 39 |

| Memory Sub-System                                                | 42 |

| Display Path Diagram                                             | 43 |

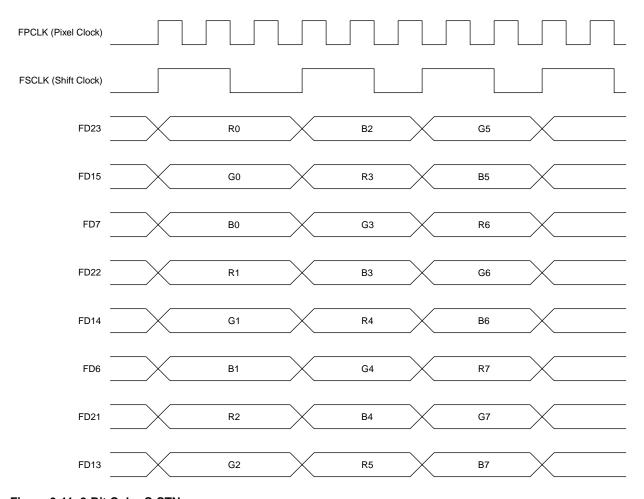

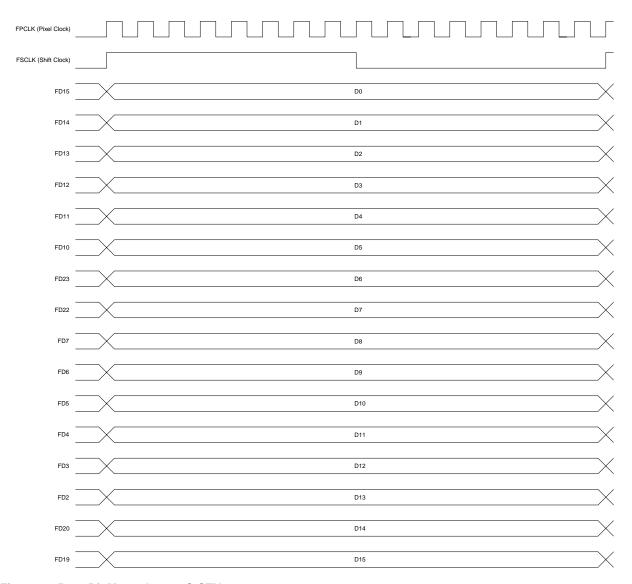

| 4-Bit Color S-STN                                                | 47 |

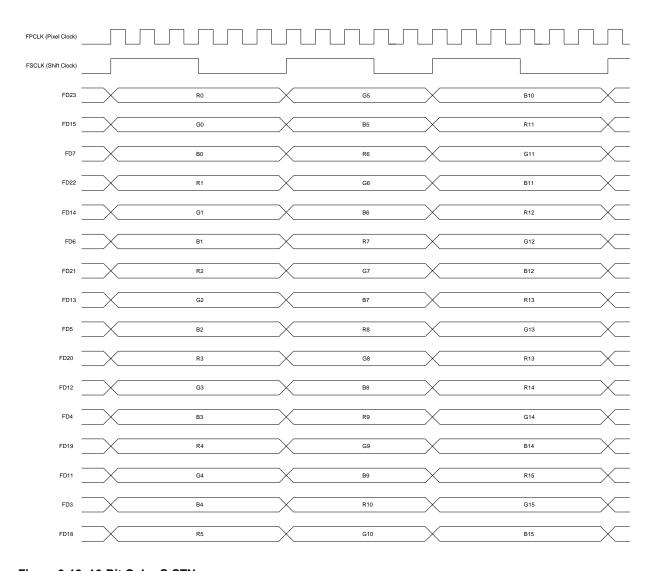

| 8-Bit Color S-STN                                                | 48 |

| 16-Bit Color S-STN                                               | 49 |

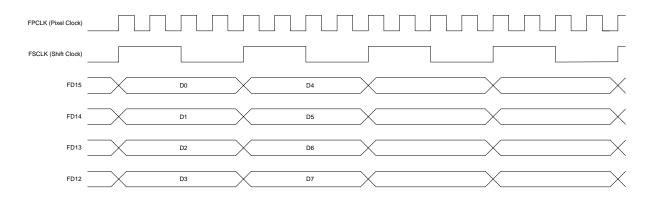

| 4-Bit Monochrome S-STN                                           | 50 |

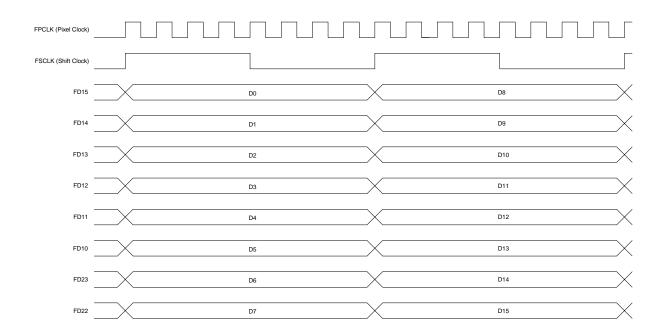

| 8-Bit Monochrome S-STN                                           | 50 |

| 16-Bit Monochrome S-STN                                          | 51 |

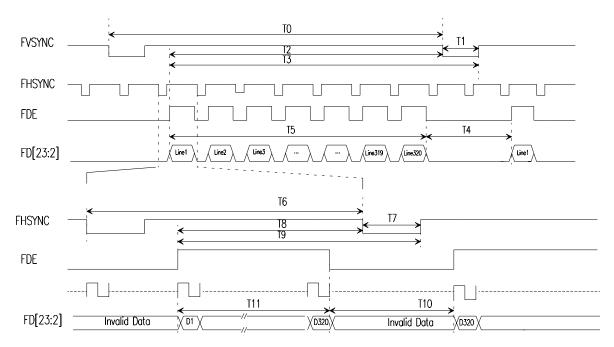

| Generic TFT Timing                                               | 52 |

| CPU Address Mapping       55         PCI Address Mapping       56         Standard PCI Configuration Space Header Type 00h       75         Display Transformation Modes       83         Address Space for Graphics Engine Registers       123         CPHA = 0 Transfer Format       206         CPHA = 1 Transfer Format       207         Chapter 5       227         Chapter 6       229         Motorola Dragonball Read       229         Motorola Dragonball Write       230         Intel SA11xx Read       231         Intel SA11xx Write       232         NEC 41xx Read       233         NEC 41xx Write       234         Hitachi SH 7750 Read       235         Hitachi SH 7750 Write       236         Hitachi SH 7700 Read       237         Hitachi SH 7700 Read       237         Hitachi SH 7700 Read       237         Hitachi SH 7700 Read       236         Hitachi SH 7700 Read       236 | Chapter 4                                   | 55  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----|

| PCI Address Mapping       56         Standard PCI Configuration Space Header Type 00h       75         Display Transformation Modes       83         Address Space for Graphics Engine Registers       123         CPHA = 0 Transfer Format       206         CPHA = 1 Transfer Format       207         Chapter 5       227         Chapter 6       229         Motorola Dragonball Read       229         Motorola Dragonball Write       230         Intel SA11xx Read       231         Intel SA11xx Write       232         NEC 41xx Read       233         NEC 41xx Write       234         Hitachi SH 7750 Read       235         Hitachi SH 7750 Write       236         Hitachi SH 7709 Read       237                                                                                                                                                                                                  | CDU Address Manning                         | 55  |

| Standard PCI Configuration Space Header Type 00h       75         Display Transformation Modes       83         Address Space for Graphics Engine Registers       123         CPHA = 0 Transfer Format       206         CPHA = 1 Transfer Format       207         Chapter 5       227         Chapter 6       229         Motorola Dragonball Read       229         Motorola Dragonball Write       230         Intel SA11xx Read       231         Intel SA11xx Write       232         NEC 41xx Read       233         NEC 41xx Write       234         Hitachi SH 7750 Read       235         Hitachi SH 7750 Write       236         Hitachi SH 7709 Read       237                                                                                                                                                                                                                                       |                                             |     |

| Display Transformation Modes       83         Address Space for Graphics Engine Registers       123         CPHA = 0 Transfer Format       206         CPHA = 1 Transfer Format       207         Chapter 5       227         Chapter 6       229         Motorola Dragonball Read       229         Motorola Dragonball Write       230         Intel SA11xx Read       231         Intel SA11xx Write       232         NEC 41xx Read       233         NEC 41xx Read       233         NEC 41xx Write       234         Hitachi SH 7750 Read       235         Hitachi SH 7750 Write       236         Hitachi SH 7709 Read       237                                                                                                                                                                                                                                                                         | ** *                                        |     |

| Address Space for Graphics Engine Registers       123         CPHA = 0 Transfer Format       206         CPHA = 1 Transfer Format       207         Chapter 5       227         Chapter 6       229         Motorola Dragonball Read       229         Motorola Dragonball Write       230         Intel SA11xx Read       231         Intel SA11xx Write       232         NEC 41xx Read       233         NEC 41xx Write       234         Hitachi SH 7750 Read       235         Hitachi SH 7750 Write       236         Hitachi SH 7709 Read       237                                                                                                                                                                                                                                                                                                                                                       |                                             |     |

| CPHA = 0 Transfer Format       206         CPHA = 1 Transfer Format       207         Chapter 5       227         Chapter 6       229         Motorola Dragonball Read       229         Motorola Dragonball Write       230         Intel SA11xx Read       231         Intel SA11xx Write       232         NEC 41xx Read       233         NEC 41xx Write       234         Hitachi SH 7750 Read       235         Hitachi SH 7750 Write       236         Hitachi SH 7709 Read       237                                                                                                                                                                                                                                                                                                                                                                                                                     | · ·                                         |     |

| CPHA = 1 Transfer Format       207         Chapter 5       227         Chapter 6       229         Motorola Dragonball Read       229         Motorola Dragonball Write       230         Intel SA11xx Read       231         Intel SA11xx Write       232         NEC 41xx Read       233         NEC 41xx Write       234         Hitachi SH 7750 Read       235         Hitachi SH 7750 Write       236         Hitachi SH 7709 Read       237                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Address Space for Graphics Engine Registers | 123 |

| Chapter 5       229         Motorola Dragonball Read       229         Motorola Dragonball Write       230         Intel SA11xx Read       231         Intel SA11xx Write       232         NEC 41xx Read       233         NEC 41xx Write       234         Hitachi SH 7750 Read       235         Hitachi SH 7750 Write       236         Hitachi SH 7709 Read       237                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CPHA = 0 Transfer Format                    | 206 |

| Chapter 6       229         Motorola Dragonball Read       229         Motorola Dragonball Write       230         Intel SA11xx Read       231         Intel SA11xx Write       232         NEC 41xx Read       233         NEC 41xx Write       234         Hitachi SH 7750 Read       235         Hitachi SH 7750 Write       236         Hitachi SH 7709 Read       237                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CPHA = 1 Transfer Format                    | 207 |

| Motorola Dragonball Read       229         Motorola Dragonball Write       230         Intel SA11xx Read       231         Intel SA11xx Write       232         NEC 41xx Read       233         NEC 41xx Write       234         Hitachi SH 7750 Read       235         Hitachi SH 7750 Write       236         Hitachi SH 7709 Read       237                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Chapter 5                                   | 227 |

| Motorola Dragonball Write       230         Intel SA11xx Read       231         Intel SA11xx Write       232         NEC 41xx Read       233         NEC 41xx Write       234         Hitachi SH 7750 Read       235         Hitachi SH 7750 Write       236         Hitachi SH 7709 Read       237                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Chapter 6                                   | 229 |

| Motorola Dragonball Write       230         Intel SA11xx Read       231         Intel SA11xx Write       232         NEC 41xx Read       233         NEC 41xx Write       234         Hitachi SH 7750 Read       235         Hitachi SH 7750 Write       236         Hitachi SH 7709 Read       237                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Motorola Dragonball Read                    | 229 |

| Intel SA11xx Read       231         Intel SA11xx Write       232         NEC 41xx Read       233         NEC 41xx Write       234         Hitachi SH 7750 Read       235         Hitachi SH 7750 Write       236         Hitachi SH 7709 Read       237                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                             |     |

| Intel SA11xx Write       232         NEC 41xx Read       233         NEC 41xx Write       234         Hitachi SH 7750 Read       235         Hitachi SH 7750 Write       236         Hitachi SH 7709 Read       237                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             |     |

| NEC 41xx Write       234         Hitachi SH 7750 Read       235         Hitachi SH 7750 Write       236         Hitachi SH 7709 Read       237                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                             |     |

| NEC 41xx Write       234         Hitachi SH 7750 Read       235         Hitachi SH 7750 Write       236         Hitachi SH 7709 Read       237                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | NEC 41xx Read                               | 233 |

| Hitachi SH 7750 Read       235         Hitachi SH 7750 Write       236         Hitachi SH 7709 Read       237                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                             |     |

| Hitachi SH 7750 Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                             |     |

| Hitachi SH 7709 Read237                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                             |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                             |     |

| Hitachi NH //U9 Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Hitachi SH 7709 Write                       |     |

#### Chapter 1

#### 1-1. LCD and Peripheral Controller Overview

The MQ-1100/1132 LCD and Peripheral Controller, is an integrated liquid-crystal display (LCD) and peripheral-interface controller device with embedded memory for low-cost, portable devices that require long battery life and high performance. This single-chip companion integrates key functions supporting a wide range of microprocessor interfaces. It has a high bandwidth, 64-bit wide-memory bus to the embedded SRAM. Featuring scalable bandwidths (up to 192 Mbyte per second), the MQ-1100/1132 offers design flexibility, giving OEMs the opportunity to create their products according to performance and power needs.

Three package options are offered: for the MQ-1100, there is a 100-pin thin quad flat pack (TQFP) package or a 100-pin micro ball grid array (BGA); and for the MQ-1132 there is a 132-pin micro ball-grid array (BGA). These packages make the MQ-1100/1132 family ideal for high-performance, mobile-connected platforms such as personal digital assistants (PDAs), smart phones, tablet computers, and internet appliances. A 2-D graphics engine, LCD display interface, and universal serial bus (USB) Function Controller are integrated on a single chip in either package. Additionally, the 132-pin BGA package includes USB Host Controller, I<sup>2</sup>S Audio Codec interface, Serial Peripheral Interface (SPI), support for Peripheral Component Interconnect (PCI) version 2.1, and additional General-Purpose I/O (GPIO) and LED pins.

Figure 1-1 on page 1-2 illustrates the block diagram for MQ-1100/1132.

Figure 1-1 MQ-1100/1132 Block Diagram

### Chapter 2

#### 2-1. PIN AND PACKAGE DESCRIPTIONS

#### 2.2 Pin Descriptions

Table 2-1 specifies the pin types for the MQ-1100/1132 LCD and Peripheral Controller.

TABLE 2-1: MQ-110/MQ-1132 Pin Types

| Туре | Description                                                                               |

|------|-------------------------------------------------------------------------------------------|

| I    | CMOS input pin                                                                            |

| IS   | Schmitt-Trigger CMOS input pin                                                            |

| 0    | CMOS output pin                                                                           |

| I/O  | Bi-directional CMOS input/output pin                                                      |

| IS/O | Bi-directional CMOS input/output pin with Schmitt-Trigger CMOS input pin                  |

| AP   | Analog power (AVDD) pin                                                                   |

| AG   | Analog ground (AGND) pin                                                                  |

| A    | Analog pin                                                                                |

| Al   | Analog input pin                                                                          |

| AO   | Analog output pin                                                                         |

| P    | Digital power (VDD) pin                                                                   |

| G    | Digital ground (GND) pin                                                                  |

| OD   | Open Drain Output pull-up must be provided by the central resource unless noted otherwise |

Table 2-1 through Table 2-20 provide descriptions for the MQ-1100 pins and the MQ-1132 pins.

TABLE 2-2: MQ-1100 and MQ-1132 Clock Pins

| Pin Name | Туре | MQ-1100<br>Pin<br>Number | MQ-1100<br>Ball<br>Number | MQ-1132<br>Ball<br>Number | Drive<br>(mA) | Description                                                                                                                                                                                                                                                                                                                        |

|----------|------|--------------------------|---------------------------|---------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSCFI    | AI   | 70                       | F10                       | E13                       | -             | Clock Oscillator Input When the internal oscillator is selected, an external 48-MHz fundamental mode crystal connected across the OSCFI and OSCFO pins in parallel with a 200K resistor generates the internal clocks. When the internal oscillator is bypassed, this input is tri-stated.                                         |

| OSCFO    | AO   | 71                       | E10                       | E12                       | _             | Clock Oscillator Output  When the internal oscillator is selected, an external 48-MHz fundamental mode crystal connected across the OSCFI and OSCFO pins in parallel with a 200K resistor generates the internal clocks.  When the internal oscillator is bypassed, this input can be driven by an external 1.8 volt clock source. |

| AVDDO    | AP   | 69                       | C10                       | E14                       | _             | Analog VDD for Oscillator (3.3 V)                                                                                                                                                                                                                                                                                                  |

| AGNDO    | AG   | 72                       | A10                       | D14                       | _             | Analog GND for Oscillator                                                                                                                                                                                                                                                                                                          |

TABLE 2-2: MQ-1100 and MQ-1132 Clock Pins

| Pin Name  | Туре | MQ-1100<br>Pin<br>Number | MQ-1100<br>Ball<br>Number | MQ-1132<br>Ball<br>Number | Drive<br>(mA) | Description |

|-----------|------|--------------------------|---------------------------|---------------------------|---------------|-------------|

| CVDD[4:1] | Р    | 90, 16,<br>38, 64        | A2, G1,<br>K4, G10        | A7, H2,<br>M7, H13        | -             | Core Power  |

| CGND[4:1] | G    | 88, 14,<br>36, 62        | D5, E6,<br>F6, D7         | C8, H3,<br>N7, J14        | -             | Ground      |

TABLE 2-3: MQ-1100 and MQ-1132, Reset and Mode Control Pins

|                |      | MQ-1100 | MQ-1100 | MQ-1132 | Drive  |                                                                                                                                         |

|----------------|------|---------|---------|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name       | Туре | Pin     | Ball    | Ball    | (mA)   | Description                                                                                                                             |

|                |      | Number  | Number  | Number  | (1117) |                                                                                                                                         |

| POR#           | IS   | 73      | C8      | D12     | -      | Power-On Reset (active low)                                                                                                             |

|                |      |         |         |         |        | Used to reset the MQ-1100/1132. Coming out of reset puts the                                                                            |

|                |      |         |         |         |        | device in a low-power state where all modules are disabled except                                                                       |

| PDWN#          | IS/O | 96      | F4      | B5      | 4      | for necessary registers.  Power Down (active low)                                                                                       |

| (GPIO4)        | 10,0 |         | 1 7     | Во      | _      | Configured as an input pin during and following power-on reset.                                                                         |

| , ,            |      |         |         |         |        | The functionality of this pin is determined by the state of the MD[3]                                                                   |

|                |      |         |         |         |        | pin at the trailing edge of reset.                                                                                                      |

|                |      |         |         |         |        | Used as a power-down input pin. Driving low disables the CPU                                                                            |

|                |      |         |         |         |        | interface input buffers such that external CPU activities will not con-                                                                 |

|                |      |         |         |         |        | sume power.                                                                                                                             |

|                |      |         |         |         |        | General Purpose I/O                                                                                                                     |

|                |      |         |         |         |        | When not used as a power-down pin, it can be used as GPIO 4.                                                                            |

| MD3<br>(GPIO3) | IS/O | 97      | E4      | A4      | 4      | Mode Select Bit 3                                                                                                                       |

| (GP103)        |      |         |         |         |        | Configured as an input pin during and following power-on reset.                                                                         |

|                |      |         |         |         |        | The state of this pin is latched with a transparent latch at the trailing                                                               |

|                |      |         |         |         |        | edge of the power-on reset pulse. Latched high at the trailing edge of reset, the PDWN# pin is the power-down input pin. If latched low |

|                |      |         |         |         |        | at the trailing edge of reset, the PDWN# pin is a GPIO pin. Typi-                                                                       |

|                |      |         |         |         |        | cally, a high-impedance pull-down or pull-up resistor is attached to                                                                    |

|                |      |         |         |         |        | this pin to set the mode.                                                                                                               |

|                |      |         |         |         |        | General Purpose I/O                                                                                                                     |

|                |      |         |         |         |        | After reset, this pin can be used as a GPIO pin.                                                                                        |

| MD2            | IS/O | 98      | B6      | C4      | 4      | Mode Select Bit 2                                                                                                                       |

| (GPIO2)        |      |         |         |         |        | Reserved for an extra mode.                                                                                                             |

|                |      |         |         |         |        | Upon reset, this pin is configured with its output buffer tri-stated and                                                                |

|                |      |         |         |         |        | its input buffer disabled.  General Purpose I/O                                                                                         |

|                |      |         |         |         |        | Can be used as GPIO 2.                                                                                                                  |

| MD[1:0]        | IS/O | 99, 100 | D4, D3  | A3, A1  | 4      | Mode Select Bits                                                                                                                        |

| (GPIO [1:0])   | 10,0 | 30, 100 | 5 1, 55 | 7.0,711 |        | These pins are configured as inputs both during and after power-on                                                                      |

| ]              |      |         |         |         |        | reset. They are latched with a transparent latch at the trailing edge                                                                   |

|                |      |         |         |         |        | of the power-on reset pulse to decide the mode of operation. Typi-                                                                      |

|                |      |         |         |         |        | cally, a high-impedance pull-down or pull-up resistor is attached to                                                                    |

|                |      |         |         |         |        | this pin to set the mode.                                                                                                               |

|                |      |         |         |         |        | General Purpose I/O                                                                                                                     |

|                |      |         |         |         |        | After reset, these pins can be used as GPIO 0 and GPIO 1.                                                                               |

TABLE 2-4: Additional MQ-1132 Reset and Mode Control Pins

| Pin Name           | Туре | MQ-1132<br>Ball Number | Drive<br>(mA) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------|------|------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCIMD#,<br>(GPIO5) | IS/O | N14                    | 4             | PCI Mode Select (active low)  Configured as an input both during and after power-on reset. The state of this pin is latched with a transparent latch at the trailing edge of the power-on reset pulse. If latched low at the trailing edge of reset, the PCI bus interface is selected regardless of MD[1:0]. If latched high at the trailing edge of reset, the bus interface is determined by MD[1:0]. Typically, a high-impedance pull-down or pull-up resistor is attached to this pin.  General Purpose I/O Bit 5  This pin can be used as GPIO 5 after reset. |

TABLE 2-5: MQ-1100 and MQ-1132, Hitachi SH 7709 and SH 7750 Bus Interface Pins

| Pin Name        | Туре | MQ-1100<br>Pin<br>Number                                                                      | MQ-1100<br>Ball<br>Number                                                                      | MQ-1132<br>Ball<br>Number                                                                         | Drive<br>(mA) | Description                                                                                                                                                                                                        |

|-----------------|------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CKIO            | IS/O | 42                                                                                            | K9                                                                                             | P9                                                                                                | 4             | Bus Interface Clock (66 MHz maximum) Provided by the CPU and used to clock the bus read/write activities. Also used by the CPU for generating the bus interface signals.                                           |

| BS#<br>(GPIO 7) | IS/O | 34                                                                                            | K6                                                                                             | P6                                                                                                | 4             | Bus Cycle Start (active low) Driven by the CPU for one clock to start a bus cycle. General Purpose I/O Bit 7 This pin can be used as GPIO 7,except for SH3/4 interfaces                                            |

| CS#             | IS   | 33                                                                                            | K5                                                                                             | N6                                                                                                | _             | Chip Select (active low) Driven by the CPU to select a MQ-1100/1132 device. The CPU address is only decoded when this signal is asserted.                                                                          |

| A[18:1]         | IS   | 13,15,<br>17, 18,<br>19, 20,<br>21, 22,<br>23, 24,<br>25, 26,<br>27, 28,<br>29, 30,<br>31, 32 | G2, H2,<br>H1, J2,<br>J1, J3,<br>K1, H3,<br>G3, H4,<br>J4, K2,<br>K3, G4,<br>J5, H5,<br>G5, F3 | G3, H1,<br>J1, J2,<br>J3, K1,<br>K2, K3,<br>L2, M2,<br>N1, N2,<br>P3, M3,<br>P4, M4,<br>N5, P5    | -             | CPU Address Bus  Driven by the CPU for all read/write accesses: 512 Kbyte of address space is provided.                                                                                                            |

| D[15:0]         | IS/O | 39,40,<br>45,46,<br>47,48,<br>49,50,<br>52,53,<br>55,57,<br>58,59,<br>60,61                   | J7, J8,<br>J9, H7,<br>H8, H9,<br>G6, G7,<br>G8, G9,<br>J10, E8,<br>F7, F8,<br>F9, H10          | M8, P8,<br>P10, N10,<br>M10, N11,<br>N12, P13,<br>M14, M13,<br>L13, L12,<br>K13, K14,<br>K12, J13 | 8             | CPU Data Bus  Driven by the CPU during write access and by the MQ-1100/1132, LCD and Peripheral Controller during read access. These pins are tri-stated during reset and when the CPU is disabled (powered down). |

| WE[1:0]#        | IS   | 51, 63                                                                                        | E9, C9                                                                                         | N13, J12                                                                                          | -             | Write Enable Bits (active low)  Byte enables driven by the CPU for write accesses. Ignored for CPU reads which are assumed to be 16-bit accesses.                                                                  |

TABLE 2-5: MQ-1100 and MQ-1132, Hitachi SH 7709 and SH 7750 Bus Interface Pins

| Pin Name       | Туре | MQ-1100<br>Pin<br>Number | MQ-1100<br>Ball<br>Number | MQ-1132<br>Ball<br>Number | Drive<br>(mA) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------|------|--------------------------|---------------------------|---------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RD/WR#         | IS   | 35                       | J6                        | M6                        | -             | Read/Write Driven by the CPU and valid throughout the bus cycle, driven high for read access and driven low for write access.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RDY#,<br>WAIT# | OD   | 41                       | К8                        | N8                        | PCI           | SH7750 Ready (active low)  Normally pulled-down by an external resistor. The MQ-1100/1132, LCD and Peripheral Controller drives this signal inactive (high) at the appropriate time during CPU read/write access to request additional wait states. After being driven high, RDY# will be driven (low) for one clock then tri-stated.  SH7709 Wait (active low)  Normally pulled-up by an external resistor. The MQ-1100/1132, LCD and Peripheral Controller drives this signal active (low) at the appropriate time during CPU read/write access to request additional wait states. Being driven low, WAIT# will be driven inactive (high) for one clock, then tri-stated. |